我覺得到 always 就可以開始寫一些有趣的事情了

一樣我們先從簡單的開始說起

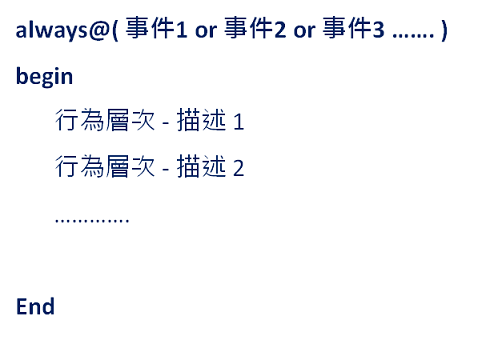

always的用法

舉個例子

always@( 事件1 )

begin

行為描述 1

End

只要事件1 發生 那就會進去 行為描述 1

always 常見的:

always@(A): A 的信號有改變就觸發

always@(A or B): A 或 B 的信號有改變就觸發

always@(Clk): Clk 時脈信號有改變就觸發

always@(Posedge Clk): Clk 時脈信號 上緣 觸發

always@(negedge Clk): Clk 時脈信號 上緣 觸發

( Posedge 就很簡單單 Pos edge 正 邊緣 )

( negedge 就很簡單單 neg edge 負 邊緣 )

來個簡單的程式看看,這是我隨便寫的 寫錯記得跟我講

module Test_always1(A,B,Out1,Out2);

input A , B ;

output Out1;

output Out2;

reg Out2;

xor(Out1 , A , B) ;

always@( A )

begin

if(Out1 == 1)

begin

Out2 = 1 ;

end

else

begin

Out2 = 0 ;

end

end

endmodule

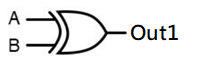

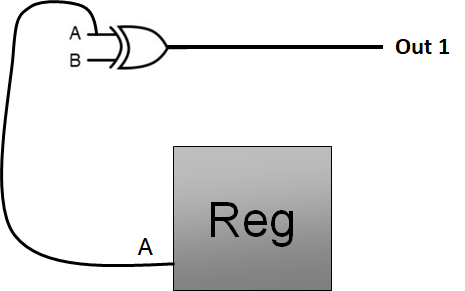

簡單思考一下這程式是甚麼,我覺得 verlog 最重要的是學會畫圖,所以我們來畫一下

輸入了一個 A、B

A跟B 接到一個 xor 輸出 Out1

有一個暫存器,如果 A 有打開

如果 A 有打開,那就會輸出 Out2

大概長這樣吧

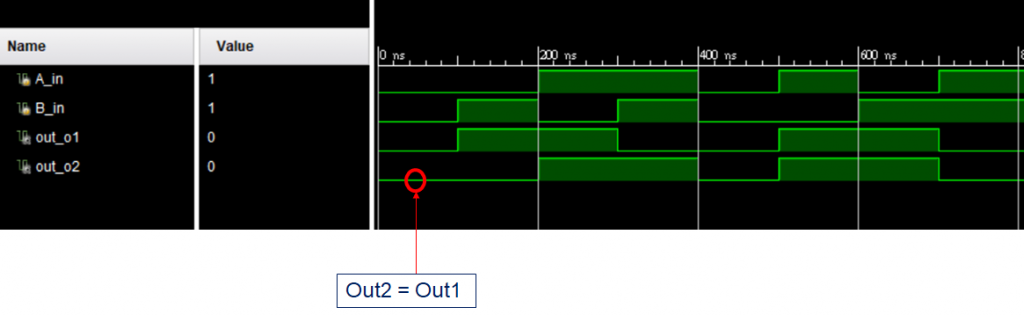

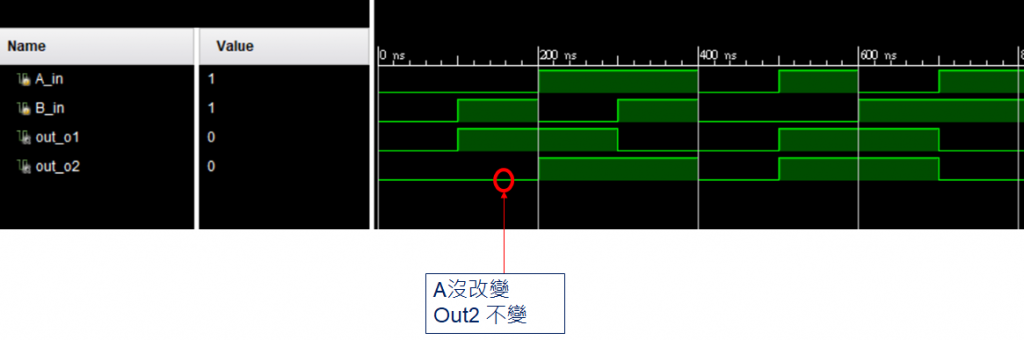

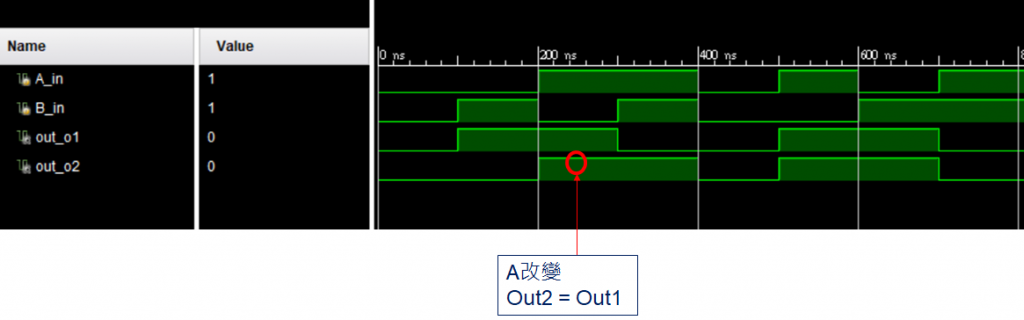

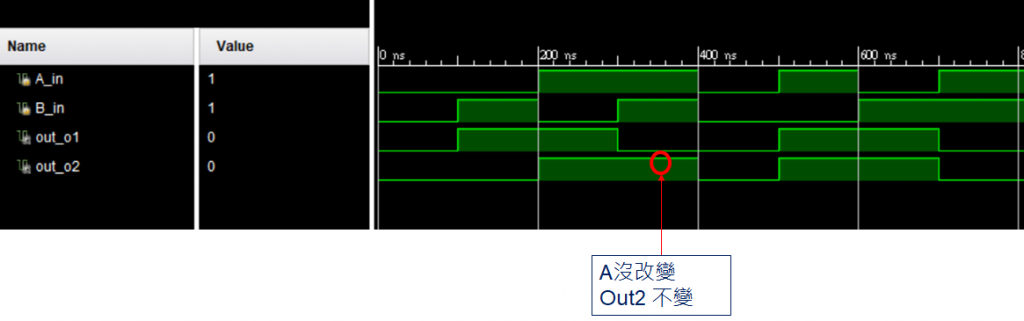

簡單來講

Out1 就是 A B 的 Xor

如果 A 有改變

Out2 = Out1

如果 A 沒有改變

Out1 維持一樣

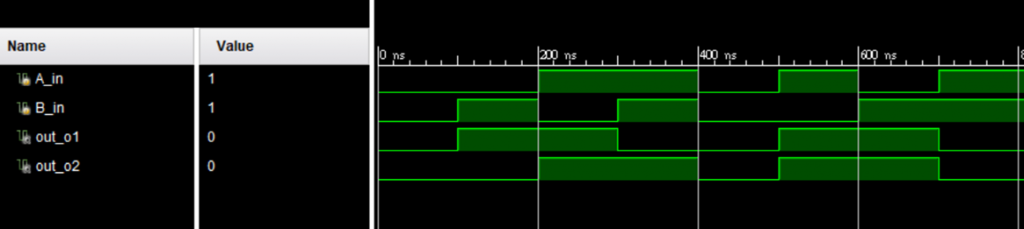

再來就是 tb

module tb1();

reg A_in , B_in;

wire out_o1 ;

wire out_o2;

Test_always1 test(

.A(A_in),

.B(B_in),

.Out1(out_o1),

.Out2(out_o2)

);

initial

begin

A_in = 0 ;

B_in = 0 ;

# 100;

A_in = 0 ;

B_in = 1 ;

# 100;

A_in = 1 ;

B_in = 0 ;

# 100;

A_in = 1 ;

B_in = 1 ;

# 100;

A_in = 0 ;

B_in = 0 ;

# 100;

A_in = 1 ;

B_in = 0 ;

# 100;

A_in = 0 ;

B_in = 1 ;

# 100;

A_in = 1 ;

B_in = 1 ;

# 100;

end

endmodule

我們來分析一下吧